40f1cab7454a684bab1e4ea3d230db1bf59c7133

Squashed commit of the following: commit f0df85e2d18ff36b04443ddb23e645cbbd5bfa58 Author: kuwoyuki <kuwoyuki@cock.li> Date: Wed Oct 16 01:36:26 2024 +0600 fix: SPI DMA wait for SPI TXE and BSY flags, also fix korean lib commit a16b9f769807a78803ba1d7cd10a4a4843827bb2 Author: kuwoyuki <kuwoyuki@cock.li> Date: Tue Oct 15 21:09:59 2024 +0600 moar log commit 0c457e17ffb956cb5fbbc40865e62f8acf8f2eea Author: kuwoyuki <kuwoyuki@cock.li> Date: Tue Oct 15 14:09:31 2024 +0600 _ commit a0b6820bc1312e429d04bf0bb39bc2a8b234cfc5 Author: kuwoyuki <kuwoyuki@cock.li> Date: Tue Oct 15 13:55:24 2024 +0600 rewrite w/o interrupts commit 83c2ab75b326be098bc15698d77ab650b14613e0 Author: kuwoyuki <kuwoyuki@cock.li> Date: Tue Oct 15 13:01:41 2024 +0600 dma config commit d871fef77d7c1838ac84f02a499f5555f78bc9ce Author: kuwoyuki <kuwoyuki@cock.li> Date: Tue Oct 15 04:47:23 2024 +0600 more dma

ch32-node fw

fw for a ch32v203 node w/ w5500 ethernet

current

SysTick IRQ and DMA issue

Enabling the SysTick IRQ leads to a permanent hang of the socket.

- With a 1ms IRQ interval, the hang occurs at

DHCP_ACKduring thecheck_DHCP_leasedIP->sendto()ARP request. - With a 100ms interval, the hang occurs during the DNS request.

- With a 1s interval it works

- Disabling SPI DMA solves it (just commenting out

reg_wizchip_spiburst_cbfunc), so it's most likely DMA related? - SPI DMA only works with prescalers 8 and 64?

- Also, for some reason it needs a ~50ms delay before configuring w5500 when compiled with

-O0, not needed with-Os...

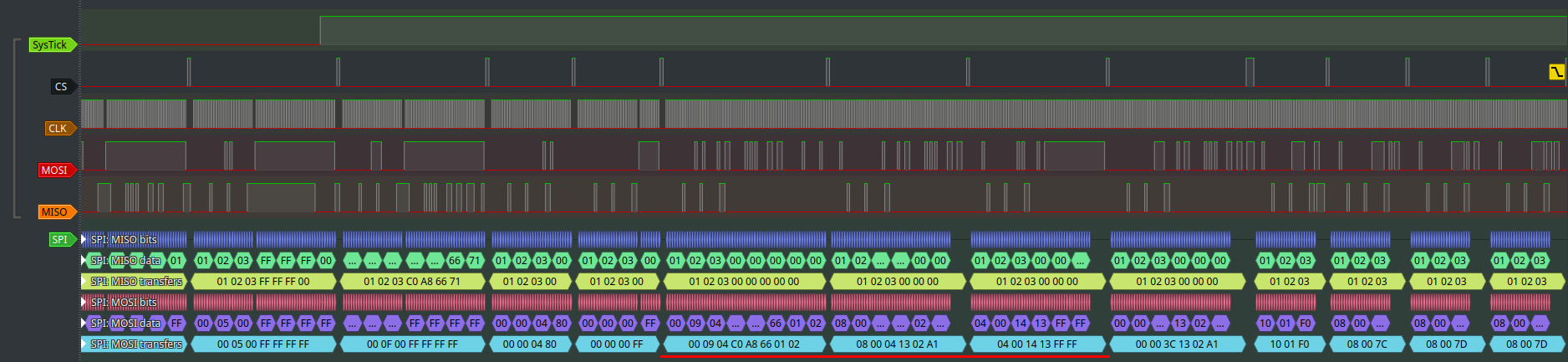

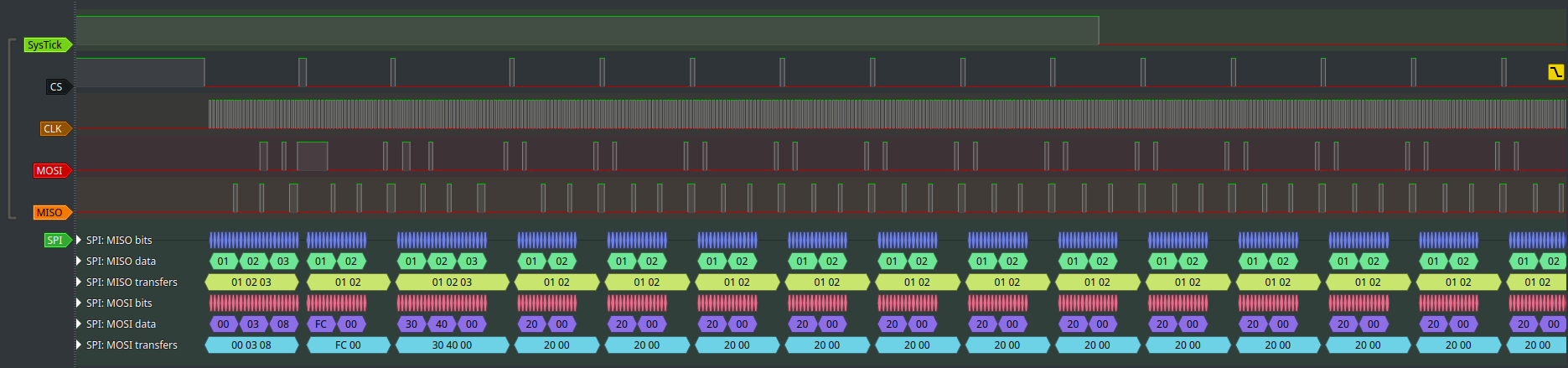

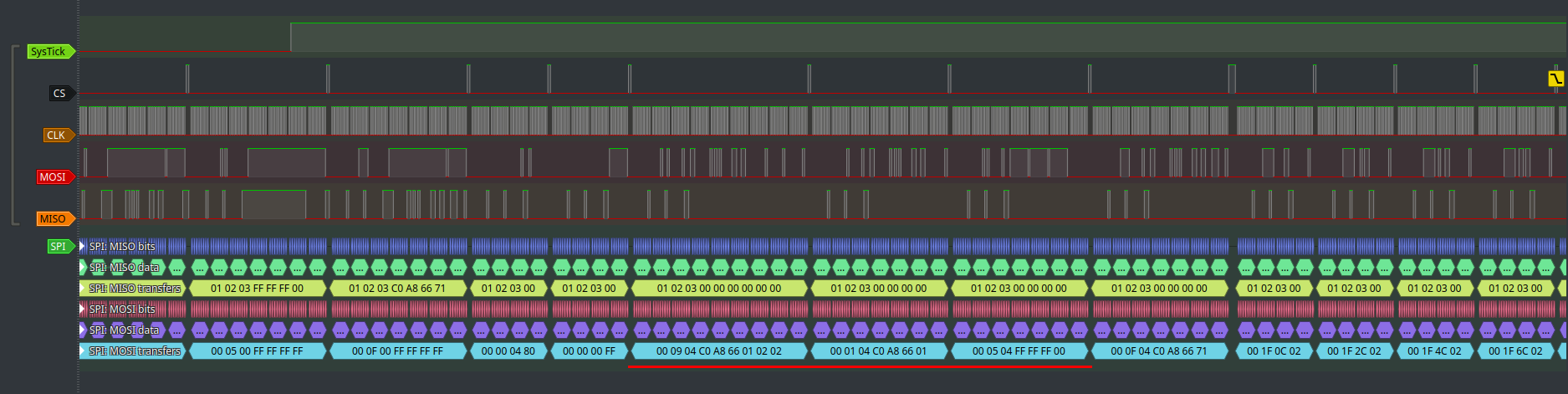

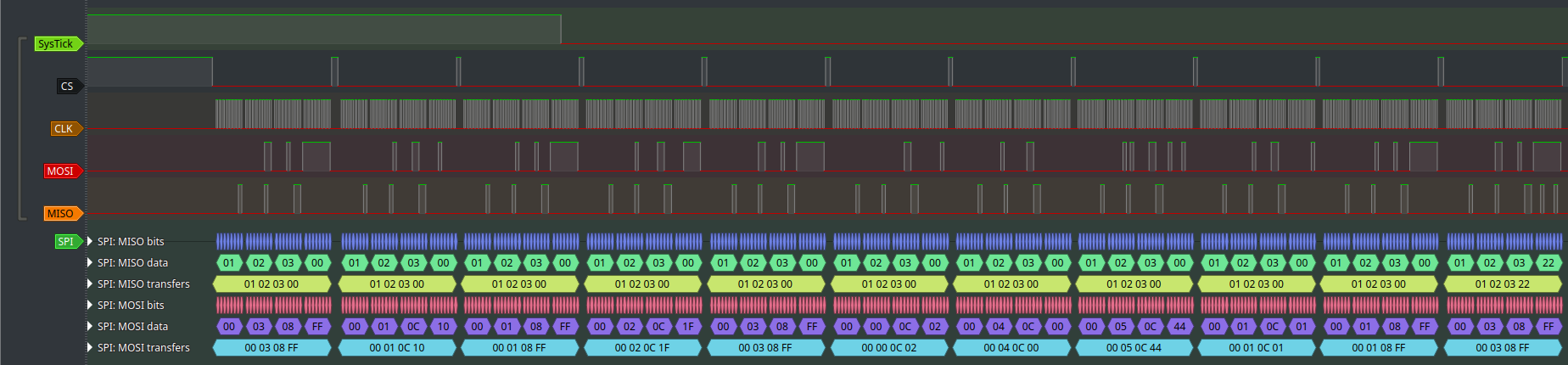

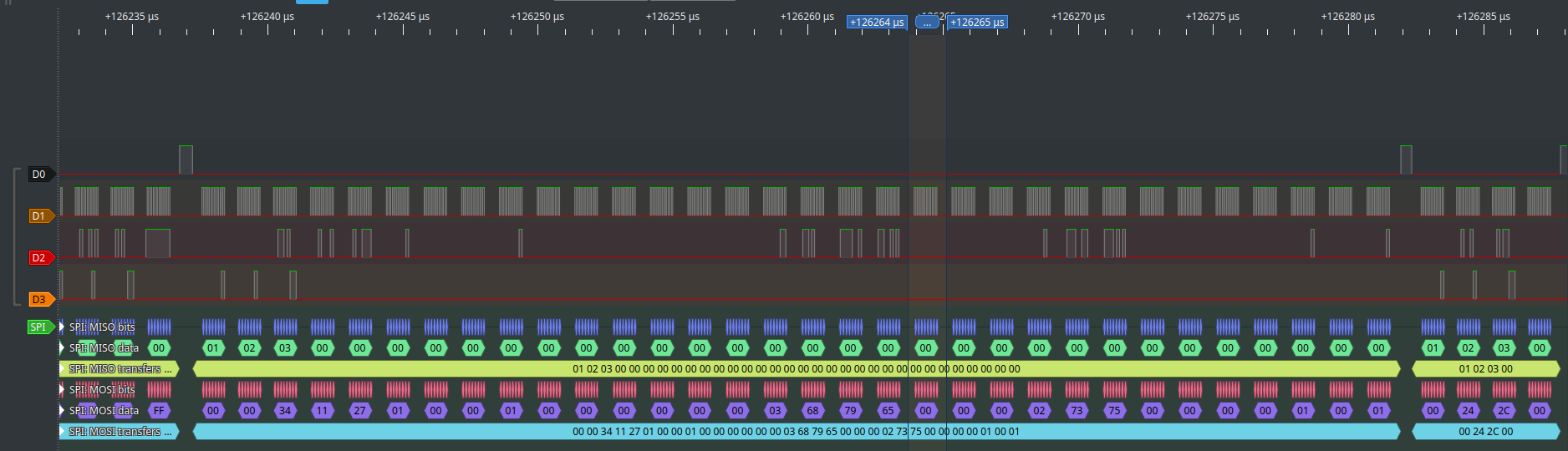

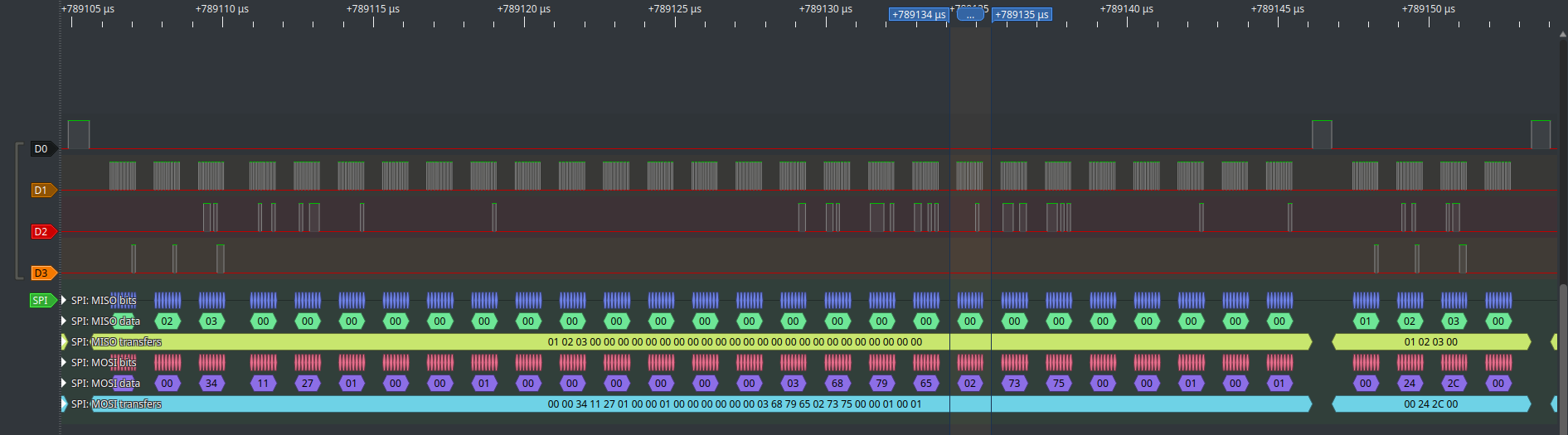

Diff between SPI w/ and w/o DMA:

SPI DMA

SPI

00 09 04 C0 A8 66 01 02 00 09 04 C0 A8 66 01 02 02

previous (DNS Processing)

solved by patching the korean bloatlib (dns_makequery in DNS.c)

w/ ch32v003fun

Partial DNS message:

11 23 81 82 00 01 00 00 00 00 00 00 03 68 79 65 00 00 00 02 73DNS_run() failed, res = 0

w/ WCH HAL (none-os).. I get a full response

Receive DNS message from 192.168.102.1(53). len = 56 Partial DNS message:

11 23 81 80 00 01 00 02 00 00 00 00 03 68 79 65 02 73 75 00 00 01 00 01 C0 0C 00 01 00 01 00 00 01 2C 00 04 68 15 33 7F C0 0C 00 01 00 01 00 00 01 2C 00 04 AC 43 B4 9AResult: 172.67.180.154

RCC_CTLR, GPIO Registers, SPIx_CTLR1 registers are identical

LA

ch32v003fun

00 00 34 11 27 01 00 00 01 00 00 00 00 00 00 03 68 79 65 00 00 00 02 73 75 00 00 00 00 01 00 01

- 32 bytes long

- (Post

68 79 65):00 00 00 02 73 75 00 00 00 00 01 00 01

none-os

00 00 34 11 27 01 00 00 01 00 00 00 00 00 00 03 68 79 65 02 73 75 00 00 01 00 01

- 27 bytes long

- (Post

68 79 65):02 73 75 00 00 01 00 01

Description

Languages

C

97.6%

Assembly

2.1%

Makefile

0.3%